# SIMULADOR PARA EL NODO DE CONMUTACIÓN ATM

Néstor Misael Peña Traslaviña\*

Alexander Forero A.\*\*

#### RESUMEN

Este artículo muestra los resultados del estudio de los nodos de conmutación "switches" multiestado ATM, con topologías de construcción Banyan, con manejo de memoria estática y compartida, localización de las colas a la entrada-salida de cada uno de los puertos y "switch" elemental (SE) de 2x2 ó 4x4. Se aplican diferentes técnicas de administración de memoria como "Backpressure", "Pushout", "Restricted Backpressure" y "Delay Pushout". En cuanto a las fuentes de entrada se simuló tráfico regular con un proceso de Bernoulli y tráfico tipo ráfaga mediante un proceso interrumpido de Bernoulli (IBP) y una fuente ON-OFF. Para realizar el estudio se implementó una herramienta de simulación, mediante la técnica de eventos discretos y el simulador fue validado con varias publicaciones.

# PALABRAS CLAVE

•"Switch" ATM, •Memoria compartida, •Red Banyan, •Red multiestado, •"Backpressure",

•"Delay Pushout", •"Restricted Backpressure", • "Pushout", •Simulación por eventos discretos.

#### 1. Introducción

Debido a la complejidad que se tiene en el estudio analítico de las características de desempeño de los "switches" ATM, las técnicas de simulación brindan una excelente alternativa para este tipo de estudios [1]-[2], razón por la cual se desarrolló una herramienta de simulación, con la cual se puedan estudiar las características de desempeño de las arquitecturas más comúnmente usadas en los "switches" ATM. Trabajos realizados como [3]-[7], muestran la potencialidad e interés que tiene el desarrollo de herramientas y modelos que permitan el estudio de los nodos de conmutación.

El núcleo principal del trabajo mostrado en el presente artículo, se basó en la construcción de un simulador para las redes multiestado Banyan, el cual fue realizado mediante la técnica de simulación por eventos discretos y validado con diferentes publicaciones [3]-[5]. Entre las características más importantes del simulador, se tiene que éste involucra técnicas de administración de memoria compartida como las expuestas en [3], brinda la posibilidad de seleccionar diferentes fuentes de entrada (si se desea, una diferente para cada puerto), diferentes topologías Banyan para la construcción de la red, permite seleccionar la localización de las colas, permite simular "switch"

<sup>\*</sup> Profesor Asociado, Departamento de Ingeniería Eléctrica y Electrónica, Universidad de los Andes

<sup>\*\*</sup> Ingeniero Electricista Universidad Nacional y Magíster en Ingeniería Electrónica de la Universidad de los Andes

de hasta 1024x1024 puertos construidos con "switches" elementales (SE) de 2x2 ó 4x4; todo lo anterior mediante una interfase gráfica tipo Windows, con su correspondiente sistema de ayuda.

El trabajo realizado, recopila lo ya hecho en [3], [4] y [8], en donde para una arquitectura de red dada, se estudian algunos parámetros de desempeño bajo fuentes tipo ON-OFF, IBP y Bernoulli respectivamente. El valor agregado con el cual cuenta el simulador, es que permite (para diferentes arquitecturas) realizar estudios comparativos de las variables de desempeño, bajo diferentes tipos de fuentes, además que brinda la posibilidad de obtener el comportamiento de las colas, mediante histogramas de longitud y tiempo de espera en fila.

El diseño y posterior desarrollo del simulador estuvo enmarcado en dos grandes etapas, la primera de ellas fue la construcción y validación de la herramienta teniendo como punto de referencia lo ya logrado en los trabajos [3]-[5], y la segunda, en la exploración de nuevas configuraciones que permitieran ayudar a conocer mejor el comportamiento de las redes multiestado Banyan, las cuales son ampliamente usadas en la tecnología ATM.

Este artículo se encuentra organizado de la siguiente manera: En la sección 2 se describe las características del simulador tales como las topologías de red Banyan, localización de las colas, esquemas de manejo de memoria, parámetros de desempeño y modelos de tráfico implementados; en el numeral 3 se describen las simulaciones realizadas y se muestra y analiza los resultados; finalmente en el aparte 4 se presentan las conclusiones y recomendaciones.

#### 2. CARACTERÍSTICAS DEL SIMULADOR

A continuación se presentan las características constructivas y de selección que se disponen en el simulador.

#### 2.1 Arquitectura del Switch.

ATM es en esencia la culminación de todos los desarrollos hechos en la conmutación de circuitos y de paquetes en los últimos 20 años. Debido al uso de paquetes de información de longitud pequeña y fija, el procesamiento del encabezado se redujo, redundando esto en un aumento de las velocidades de transmisión. En cuanto al transporte de las celdas, el nodo de conmutación debe combinar tres funciones principales, la conmutación, la multiplexación y concentración y por último la demultiplexación y expansión.

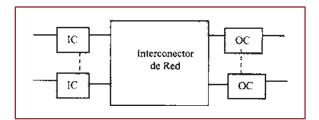

Para llevar a cabo estas tareas es necesario un "switch fabric", el cual está implementado con uno o varios "switches elementales" (SE), los cuales consisten en un interconector de red, un controlador de entrada (IC) para cada línea de entrada y un controlador de salida (OC) para cada línea de salida, como se muestra en la Fig. 1.

**Figura 1.** Modelo general para un "switch" elemental.

El arribo de las celdas es sincronizado por un reloj interno del IC, el OC transporta las celdas, las cuales han sido recibidas del interconector de red y las lleva al puerto de salida [4], [9].

Basados en los "switches" elementales (SE) es posible construir redes de tamaño NxN, conocidas como redes multiestado, dichas redes pueden ser clasificadas en redes **con** y **sin** bloqueo. Las redes multiestado Banyan son arquitecturas que se encuentran catalogadas dentro de las redes multiestado con bloqueo interno [10].

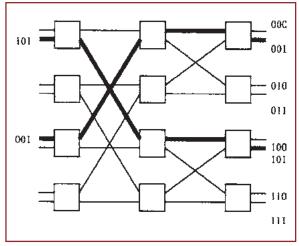

Las redes Banyan tienen la característica de ser autoenrutadas, esto se logra evaluando el bit correspondiente al número del estado en que se encuentra el paquete de información y conmutándolo a éste. La fig. 2 muestra la trayectoria de una ruta obtenida de ésta manera.

Figura 2. Switch Banyan autoenrutado

El número de estados para un switch NxN construido con SE de tamaño bxb esta dado por log<sub>b</sub>N, en donde cada uno de estos estados esta formado por N/b SE [8], [10], es decir para un "switch" de 16x16 construido con SE de 2x2 es necesario una red de cuatro estados, con ocho SE en cada estado.

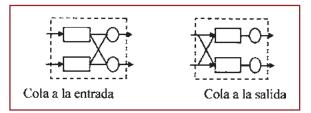

En cuanto a la ubicación de las filas dentro de los SE, estas pueden encontrarse a la entrada o salida de cada uno de los puertos como se muestra en la fig. 3.

**Figura 3.** Localización de las colas del SE 2x2.

Las gráficas representan la ubicación de las colas en un "switch" elemental (SE) 2x2. Para el modelo de cola a la entrada, cada servidor esta conectado a dos colas, y en el caso que las

celdas que encabezan las dos filas requieran ser atendidas por el mismo servidor, éste es quien elige aleatoriamente a quien atender.

Muchas tecnologías para las redes Banyan han sido propuestas [8], [10]-[11], siendo la diferencia entre ellas la forma de interconexión de los SE entre estados adyacentes. El anexo 1 muestra la estructura de cuatro diferentes redes con N=16, que pueden también ser usadas en forma inversa, es decir el último estado se convierte en el primero.

# 2.2 Esquemas de Manejo de Memoria Compartida.

Independientemente de la ubicación de las filas, el tamaño de la cola puede tener un valor constante o variable; una forma de que el tamaño de las filas sea flexible es implementando la técnica de memoria compartida, que consiste en compartir una misma memoria de tamaño **M** (constante) entre los diferentes puertos que componen el SE.

Dentro de la técnica de memoria compartida, existen varios esquemas de administración y manejo de la memoria, las cuales se explican a continuación:

NC: "No Controls". Consiste en que cada SE tiene una memoria compartida de M celdas para sus b colas, sin ningún tipo de restricción.

PO: "Pushout". Las celdas arriban sin restricción alguna hasta cuando la memoria se encuentra llena (cola=M), cuando la memoria este llena, la celda entrante sacara a la celda que encabece la cola más larga; es claro que no necesariamente ocupara espacio en dicha cola y su posición en la cola será la ultima.

**BP:** "Backpressure". Este esquema involucra el compartir memoria con otros SE's. La técnica consiste en que cuando la memoria de un SE esta llena, este envía una señal a los SE's que se encuentran conectados a él en el estado anterior, para que no envíen más celdas. Es claro

que usando esta técnica solo se presenta perdida de celdas en los SE's del primer estado de la red.

RBP: "Restricted Backpressure". Este esquema es una mejora para el BP y consiste en que cuando es recibida la señal memoria llena de un SE (estado i) los SE's (estado i-1) que están conectados a él, dejan de enviar celdas hasta cuando se llegue a un valor preestablecido de T para la memoria de los SE's del estado i-1, y superado este valor, se vuelve a servir celdas sin ninguna restricción.

DOP: "Delay Pushout". Esta técnica es una combinación del RBP y PO. Se comporta como un RBP con la diferencia que cuando los SE's (estado i-1) comienzan a servir celdas nuevamente (El valor de ocupación de la memoria es superior a T) estas ocuparan el espacio en memoria de la celda que encabece la cola mas larga en el SE (estado i), como lo hace la técnica PO.

Es importante mencionar que la disciplina de la fila es FIFO, ya sea cuando se use memoria estática (constante para cada puerto) o compartida (en cualquiera de sus esquemas de administración).

#### 2.3 Parámetros de Desempeño.

En la herramienta desarrollada es posible seleccionar parámetros de desempeño como longitud media de la fila, tiempo medio de espera en fila, probabilidad de pérdida de celdas y tráfico cursado. Estos resultados son dados para cada uno de los puertos en cada estado. Además es posible realizar un estudio del comportamiento de las filas en cuanto a longitud y tiempo de espera se refiere, ya que también es factible seleccionar histogramas de estos comportamientos.

#### 2.4 Modelos de Tráfico.

Las fuentes implementadas en el simulador para ser aplicadas a los puertos de entrada son: **Proceso de Bernoulli.** El arribo de las celdas a cada uno de los puertos de entrada, se da mediante una variable aleatoria de Bernoulli con probabilidad **p**. Cada una de las celdas de entrada, tiene igual probabilidad de tener como destino cualquier puerto de salida [4].

IBP (Interrupted Bernoulli Process). Este es un modelo en el cual los arribos son más frecuentes durante ciertos periodos de tiempo (estado activo), pero también existen periodos de desocupación en donde no se presenta llegada alguna de celdas (estado inactivo); por lo tanto la probabilidad de tener secuencias de arribo en cada tiempo de celda aumenta en este tipo de proceso.

La caracterización de la fuente se encuentra especificada por dos estados, denominados estado **activo** e **inactivo**, los cuales ocurren uno seguido del otro. El tiempo de duración de cada uno de los estados, está dado por una variable aleatoria geométricamente distribuida, y el arribo de las celdas en el estado activo obedece a un proceso de Bernoulli [4].

Un IBP esta gobernado por una cadena de Markov de dos estados, es decir dado que el proceso se encuentra en el estado activo, éste permanecerá en dicho estado con probabilidad p, o cambiará al estado inactivo con probabilidad 1-p; por otra parte si el proceso se encuentra en el estado inactivo, éste permanecerá en él con una probabilidad q, o cambiara al estado activo con probabilidad 1-q. En el estado activo arribara una celda al puerto de entrada de acuerdo a una variable aleatoria de Bernoulli con probabilidad α.

Por lo anterior se tiene que el tráfico de una fuente IBP y el coeficiente de variación de la media entre arribos esta dado por [4]:

$$\rho = \alpha \frac{1-q}{2-p-q}, \qquad C^2 = 1 + \alpha \left( \frac{(p+q)(1-p)}{(2-p-q)^2} - 1 \right)$$

Es importante mencionar que cada una de las celdas de entrada, tiene igual probabilidad de

tener como destino cualquier puerto de salida. **Fuente ON – OFF.** Al igual que una fuente IBP, la fuente ON-OFF se encuentra dominada por dos estados. La duración de los estados activo e inactivo obedece a una variable aleatoria Geométricamente distribuida con parámetros  $\alpha$  y  $\beta$  respectivamente.

En el estado activo, las celdas arriban consecutivamente en cada tiempo de celda y tienen igual probabilidad de tener como destino todos los puertos de salida. Aquí es importante mencionar que todas las celdas en el mismo tiempo activo están dirigidas al mismo puerto de salida. Se asume que en el periodo activo, arriba al menos una celda, pero la duración del estado inactivo puede ser cero.

#### 3. SIMULACIONES.

Esta sección se encuentra dividida en dos partes, la primera esta constituida por las simula-

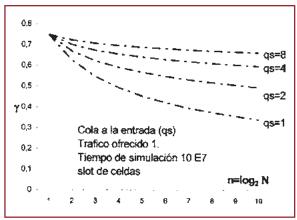

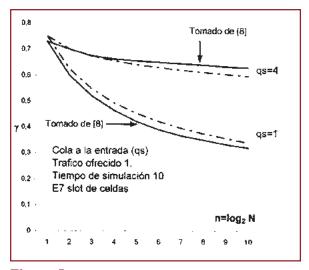

**Figura 4.** Tráfico cursado (y) en función del tamaño del "switch".

Las Fig. 4 y 5, representan el tráfico cursado en función del tamaño del "switch". La diferencia entre las curvas simuladas y las de la referencia pueden ser atribuibles al tiempo de simulación usado.

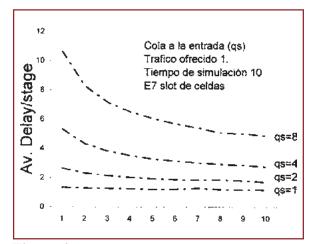

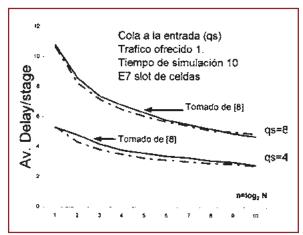

Las Fig. 6 y 7, representan el retardo promedio por estado dado en T/n, en función del tamaño del "switch". Para este parámetro, la diferencia entre la referencia y las simulaciones, ciones realizadas para validar el simulador, tomadas de los trabajos realizados en [3], [4] y [8], la segunda parte corresponde a simulaciones que buscan explorar la potencialidad de la herramienta y a su vez realizar un estudio de desempeño de las redes Banyan, teniendo como variable el tipo de fuente.

Las simulaciones se desempeñan en el tiempo discreto, teniendo como unidad de tiempo un "slot" de celda. Por lo tanto todos los tiempos y retardos son medidos en esta unidad.

# 3.1 Validación del Simulador.

Las siguientes son las simulaciones que se realizaron para la validación del simulador.

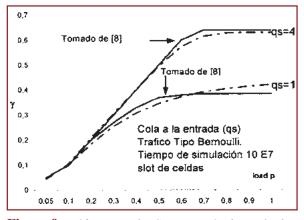

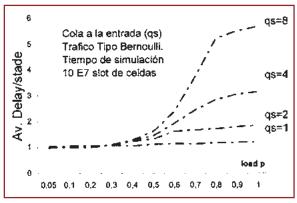

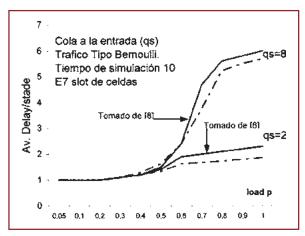

Caso 1 [8]. Redes Banyan multiestado de 2x2 hasta 1024x1024, construidas con SE 2x2 con cola a la entrada. Estudio del comportamiento del tráfico cursado y retardo promedio por estado, para diferentes longitudes de cola.

**Figura 5.** Tráfico cursado (g) comparación de resultados.

es menor que la presentada para el tráfico cursado.

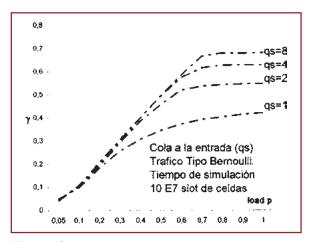

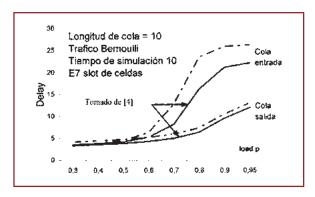

Caso 2 [8]. Red Banyan multiestado de 64x64, construida con SE 2x2 con cola a la entrada. Estudio del comportamiento del tráfico cursado y retardo promedio por estado, para diferentes longitudes de cola.

Las Fig. 8 y 9, representan el tráfico cursado en función del tráfico ofrecido. La diferencia entre las curvas simuladas y las de la referencia, pueden ser atribuible al tiempo de simulación usado.

Las Fig. 10 y 11, representan el retardo promedio por estado dado en T/n, en función del tráfico ofrecido. Para este parámetro, la diferencia entre la referencia y las simulaciones, es un poco mayor que la presentada para el tráfico cursado. El error promedio en cualquiera de los casos no es mayor al 7%.

Figura 6. Retardo promedio.

**Figura 7.** Retardo promedio. Comparación de resultados.

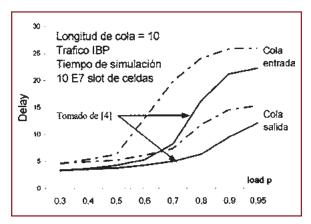

Caso 3 [4]. Red Banyan multiestado de 8x8, construida con SE 2x2 con cola a la entrada y salida. Estudio del comportamiento del retardo en la red, para fuentes tipo Bernoulli e IBP.

Las Fig. 12 y 13, representan el retardo total en la red en función del tráfico ofrecido. Para este parámetro, las curvas difieren significativamente para tráficos altos.

Figura 8. Tráfico cursado (g) en función del tráfico.

**Figura 9.** *Tráfico cursado. Comparación de resultados.*

Figura 10. Retardo promedio por estado.

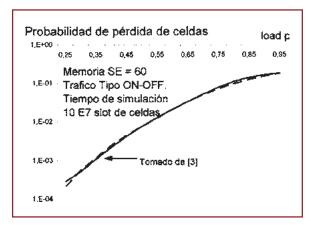

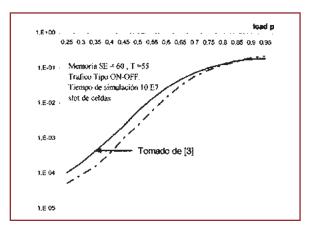

Caso 4 [3]. Red Banyan multiestado de 64x64, construida con SE 4x4 con cola a la salida, manejo de memoria compartida. Estudio del comportamiento de la probabilidad de perdida de celdas por estado y en toda la red.

La fig. 14 y 15 son apenas una muestra del total de curvas obtenidas mediante el estudio, ya que para cada uno de los estados de la red y para cada uno de los esquemas de manejo de memoria compartida se obtuvo una curva. El parámetro de estudio y comparación es la probabilidad de pérdida de celdas, la cual resultó con un error promedio no superior al 8% para todos los casos. Los errores más significativos se encontraron en la zona de tráficos bajos, ya que el orden de la probabilidad es de 10-4 celdas, los cuales pueden ser catalogados como eventos raros, pues la referencia [3]) no precisa cual fue el tiempo de simulación.

**Figura 11.** Retardo promedio. Comparación de resultados.

**Figura 13.** Retardo en la red. Comparación de resultados.

# 3.2 Simulaciones.

Los siguientes casos son una muestra del total de los escenarios simulados, que fueron planteados con el propósito de estudiar y comprender con mayor detalle el comportamiento de los parámetros de desempeño de las redes multiestado Banyan.

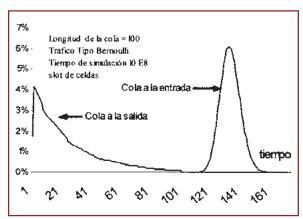

Caso 1. SE 2x2 con cola a la entrada y a la salida. Estudio del comportamiento del tiempo de espera en fila. Ver Fig. 16.

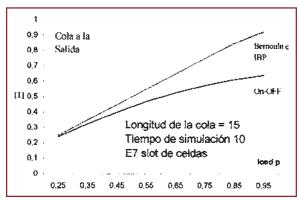

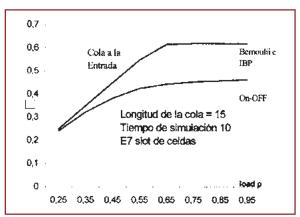

Las Fig. 17 y 18 muestran el comportamiento de una red Banyan de 256x256, teniendo como parámetro de desempeño el tráfico cursado (gð) en la red. Se observa que independiente de la localización de la cola, la fuente "On-Off" provoca un menor desempeño de la red. Las fuentes Bernoulli e IBP siguen un mismo comportamiento.

Caso 2. Red Banyan multiestado de 256x256, construida con SE 4x4 con cola a la entrada y salida. Estudio del comportamiento del tráfico cursado y retardo en la red, para diferentes tipos de fuente.

**Figura 12.** Retardo en la red. Comparación de resultados.

**Figura 14.** Probabilidad perdida de celda, para el esquema de memoria compartida tipo PO. Comparación de resultados.

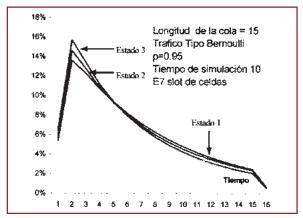

Caso 3. Red Banyan multiestado de 64x64, construida con SE 4x4 con cola a la salida. Estudio del comportamiento de la longitud y tiempo en fila, para diferentes tipos de fuente. Como muestra de este estudio se presenta la Fig. 19, que representa el tiempo de espera en

Figura 16. Histograma tiempo de espers en fila.

**Figura 18.** Tráfico cursado para un "switch" 256x256, bajo diferentes tipos de fuente.

**Figura 15.** Probabilidad perdida de celda, para el esquema de memoria compartida tipo DPO. Comparación de resultados.

fila, correspondiente a un tráfico de 0.95 con un proceso de Bernoulli. Se observa que para los diferentes estados de la red el comportamiento es similar y muy parecido al presentado en el caso 1, el cual corresponde a un "switch" elemental (SE) 2x2 con cola a la salida.

**Figura 17.** Tráfico cursado para un "switch" 256x256, bajo diferentes tipos de fuente.

**Figura 19.** Histograma tiempo de espers en fila para una red Banyan de 64x64 construida con SE 4x4.

### 4. Conclusiones

Se implementó una herramienta de simulación, mediante la técnica de eventos discretos, para realizar el estudio de los parámetros de desempeño de las redes Banyan multiestado, el simulador fue validado con varias publicaciones, arrojando excelentes resultados. La herramienta construida recopila en sí, todas las características y potencialidades de los diferentes simuladores realizados en las publicaciones que sirvieron como referencia, y además brinda características adicionales en cuanto a la interfase con el usuario se refiere, ya que por ser implementada en ambiente Windows, permite un fácil manejo, además de contar con un sistema de ayuda que facilita la manipulación y entrada de los datos.

Como resultado del proceso, y en cuanto a los parámetros de desempeño se refiere, se comprobó que la localización de las colas juega un papel importante en el desempeño del "switch", siendo la mejor, la ubicación de la cola a la salida. En cuanto al manejo de la memoria, las técnicas de memoria compartida resultan ser mejores que cuando es asignada una memoria fija a cada fila. Dentro de los esquemas para el manejo de la memoria compartida se tiene que la técnica DOP es la que la que presenta un mejor desempeño, pues para las simulaciones realizadas siempre obtuvo los valores más bajos en cuanto a probabilidad de pérdida se refiere. A la vista de los resultados, las redes construidas con "switch" elementales (SE) 4x4 muestran un mejor desempeño que las construidas con SE 2x2, debido al numero de estados que cada una de ellas emplea.

En cuanto a los modelos usados para las fuentes, se tiene que los modelos tipo ráfaga dan como resultado un decremento en las características de desempeño del "switch" en comparación con el modelo de tráfico regular (Bernoulli). Comparando el desempeño de las redes bajo los dos modelos de tráfico tipo ráfaga (IBP y ON-OFF), se tiene que es más crítico la fuente ON-OFF.

Para futuros trabajos, se propone complementar la herramienta implementando otras disciplinas de fila, diferente a la FIFO, también es posible adicionar otros tipos de fuentes más representativas de las redes ATM, tales como la voz y el video.

# 5. REFERENCIAS

- [1] G. N. Higgingbotton, «Performance Evaluation of Communication Networks», Artech House, 1998.

- [2] R. Sheldon, "Simulation", Academics Press, Segunda Edición, 1997.

- [3] D. Basak and others, «Sharing Memory in Banyan-Based ATM Switches», IEEE Journal on Selected Areas in Communications, Junio 1997, Volumen 15, Número 5. Pag 881 891.

- [4] D. Sobirk and J. M. Karlsson, «ATM Switching Structures a Performance Comparison», Department of Communication Systems, Lund Institute of Technology, Box 118, 221 00 Lund, Sweden.

- [5] F. M. Chiussi, Ye Xia, «Performance of Shared-Memory Switches UnderMulticast Bursty Traffic», IEEE Journal on Selected Areas in Communications, Abril 1997, Volumen 15, Número 3. Pag 473 487.

- [6] S.F. Oktug and M.U. Caglayan, «Desing and Perfomance Evaluation of a Banyan Network Based Interconnection Structure for ATM Switches», IEEE Journal on Selected Areas in Communications, Junio 1997, Volumen 15, Número 5.

- [7] D. Basak and others, «Sharing Memory in Banyan-Based ATM Switches», IEEE Journal on Selected Areas in Communications, Junio 1997, Volumen 15, Número 5.

- [8] M. Schwartz, "Broadband Intregrated Netwoks", Prentice Hall, 1996. Chapter 5.

- [9] R. Händel and M. N. Huber, "Intregrated Broadband Netwoks", Addison-Wesley, Tercera Edicion, 1993

- [10] P. Achille, "Switching Theory", "Architecture and Performance Broadband", Jhon Wiley, 1998.

- [11] M. Schwartz, "Redes de Telecomunicaciones: Protocolo Modelado y Analisis", Addison-Wesley, 1994.